AVR - Basteleien - Logic-Analyzer MiniLog

Da sich durch mein stšndiges Umbauen ein paar Ungereimtheiten eingeschlichen haben, bitt unbedingt in "News" reinschauen!

Vor lšngerer Zeit hatte ich mal ein Projekt angefangen: mikrocontroller.net

Durch Umzug, mangelnde Zeit und fehlender Notwendigkeit, es unbedingt fertig zu machen, blieb es letzlich erstmal liegen.

Ein Bekannter gab letztlich vor ein paar Wochen den AnstoŖ, es zumindest wieder auszugraben.

Das Display hat inzwischen eine andere Verwendung gefunden, eine Nutzung am PC erstmal nšherliegend.

Recherchen im Internet ergaben mehrere Projekte, Aufwand und/oder Software entsprachen aber irgendwie erstmal nicht meinen Vorstellungen

Als Soft- und Hardwareansatz kam LoLa in die nšhere Auswahl.

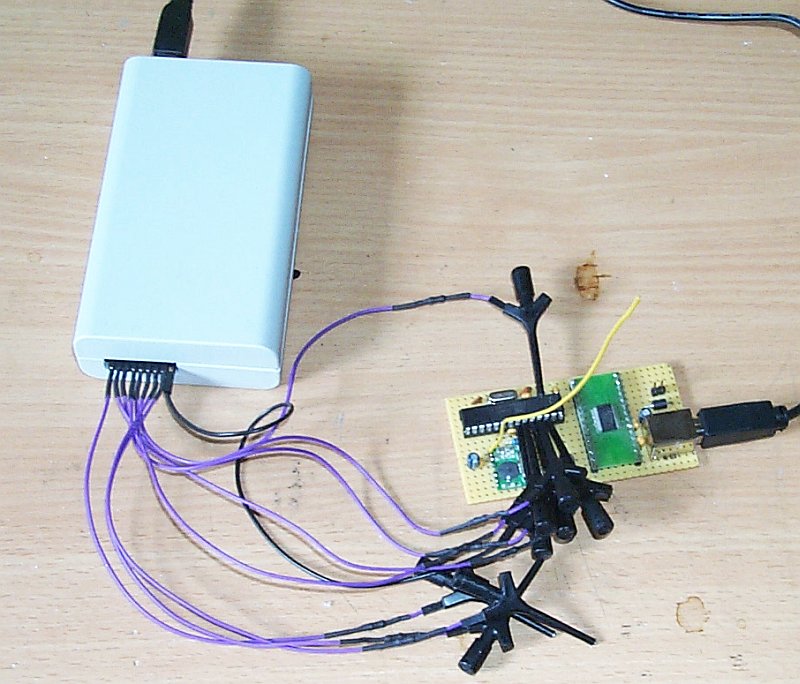

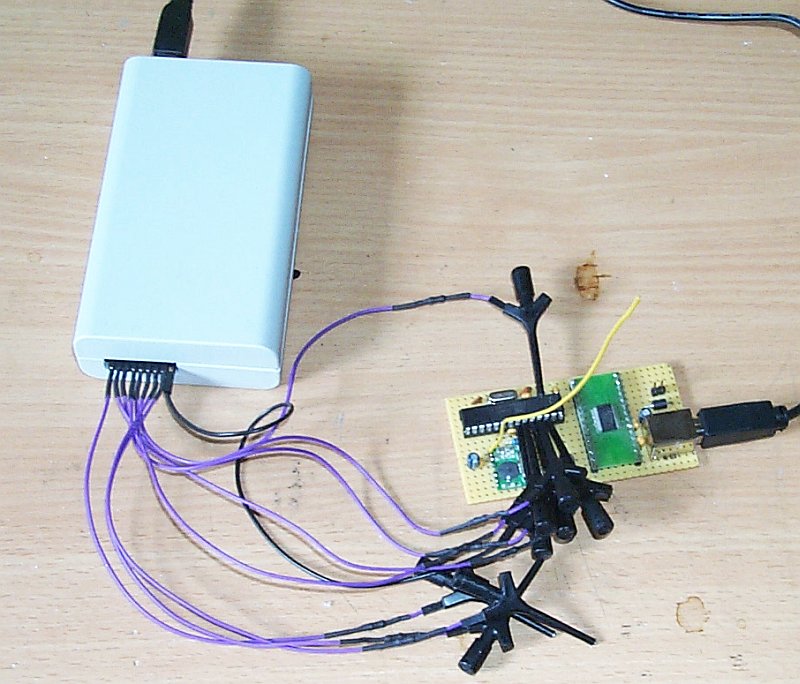

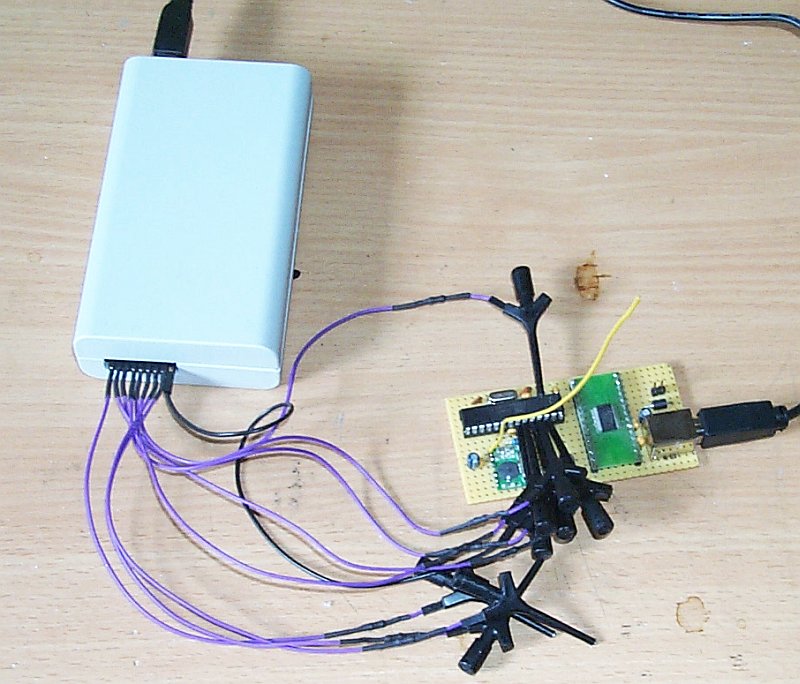

Ein schneller Testaufbau zeigt, daŖ mir der Ansatz speziell der Software und einige Ideen zur AVR-Software gefielen.

Damit stand es fest: Ansštze meiner alten Experimente mit der Software von LoLa kombinieren.

Versuche, den Autor von LoLa Łber avrfreaks.bet zu erreichen um eventuell an die Delphi-Sourcen zu mommen, schlugen leider fehl.

Ein erster Aufbau war auf Anhieb erfolgreich, die mŲgliche Samplerate war 10MHz (20MHz Mega644, der auch den Takt erzeugte).

Jetzt war mein Ehrgeiz geweckt und es wurde nochmal umgebaut. 50MHz stabil, vielleicht sogar 80MHz...

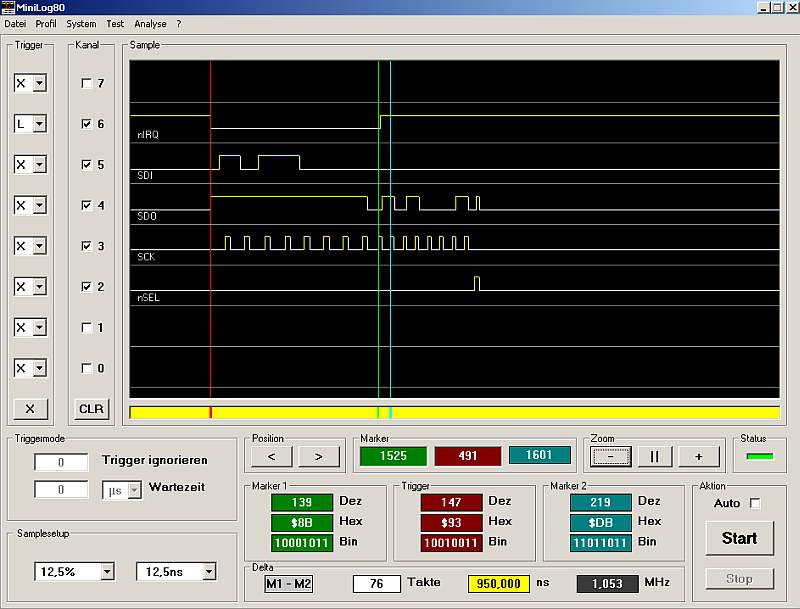

Nun stand ich aber vor dem Problem, daŖ LoLa als Software mangels Sourcen ausschied, 2k Samplespeicher und unpassende Zeiten.

AuŖerdem fehlten mir ein paar Sachen, die doch gerne eingebaut hštte.

Das Ende vom Lied: ich habe mein altes VB 6 ausgegraben und die Software selbst geschrieben...

Stand der Dinge:

Hardware:

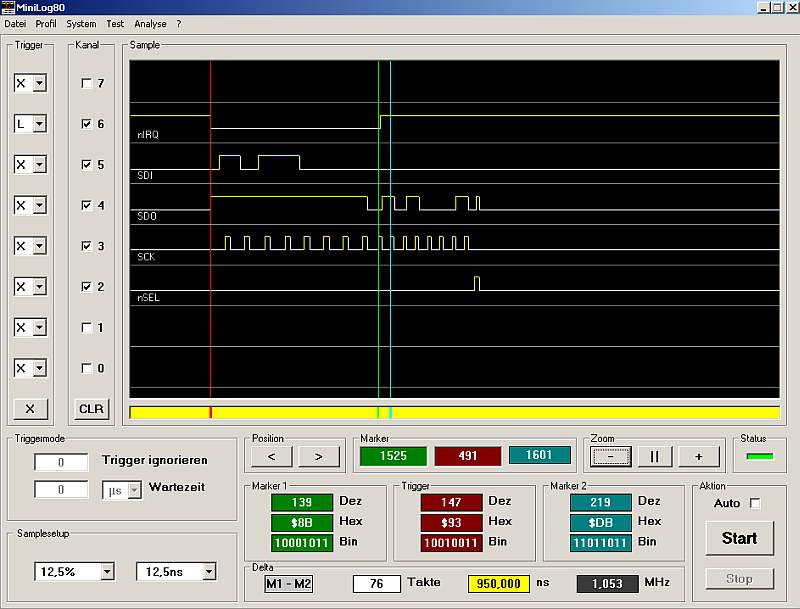

8 Kanšle, max. 50MSample/s, 16000 Sample Speicher, Trigger auf beliebige Pegelkombinationen

32k Samplespeicher ist per LŲtkolben auŖer Betrieb, da es noch Anpassungen an der PC-Software erfordert,

die Anzahl der Kanšle kŲnnte auf 16 (oder mehr...) erweitert

werden (je 8 Bit ein Cacheram und ein bi-directionaler TriState-Bustreiber).

Das ist aber vŲllig ungetestet, mŁŖte aber gehen.

80MHz Samplerate waren beim Lochrasteraufbau nicht stabil, deshalb erstmal 50MHz.

Kosten?

Teile lagen fast alle noch bei mir rum, der TTL-Kram wohl so 4 Euro,

der AVR (ja, der Mega644 ist vŲllig Łberdimesioniertm war aber der Einzige, der rumlag und mit 20MHz Takt war und genug Portpins hatte...)

Kleinkram, Quarzoszillatoren usw. usw.

Je nach Vorršten also wohl so 20 Euro. Als USB-Adapter geht jeder, der TTL kann oder man hat noch eine serielle und lŲtet einen MAX232 dran...

Aktueller Stand der Dinge:

Die ursprŁngliche Version hat jetzt einen Mega16 bekommen und eine gešnderte Takterzeugung.

Nach einer geringfŁgigen ńnderung der Zšhlerbeschaltung sind die 80MHz jetzt stabil!

08.07.2009

In beiden Schaltungen geringe ńnderungen der Steuerlogik um mit mŲglichst identischer Software auszukommen.

80MHZ Version kann jetzt mit allen 28Pin Cache-Rams bestŁckt werden (also 8-32k).

Es werden aber immer nur 4k genutzt!

Die AVR-Firmware wurde entsprechend angepasst

Es wird ddemnšchst nur noch eine AVR-Firmware geben, die per Einstellungen passend assembliert werden kann.

Auch die PC-Software wird eine Version werden, die die angeschlossene Hardware automatisch erkennt.

Es spricht auch nichts dagegen, die Takterzeugung gegeneinander auszutauschen, ob die Mega48/88 Version mit 80MHz lšuft, ist ungetestet.

Es geht da aber nur um Adresszšhler, Ram und Aufbau.

Die Firmware muŖ natŁrlich angepasst werden, ist aber wenig Aufwand, werde ich mit reinbauen.

Die Frage nach Nutzung des Mega8 statt Mega48/88 kam auch, prinzipiell mŲglich.

Anpassung wšre AVR-Takt auf 16MHz mit eigenem Quarz (es sei denn, der eigene Mega8 lšuft mit 20MHz) und der internen Tabellen.

Werde ich beim ZusammenfŁgen der AVR-Firmware mit einplanen, ob ich es teste weiŖ ich aber jetzt noch nicht.

Hardware

Stand der Software

Eagle 5.x Schaltplan liegt unter Hardware, PC-Software und AVR-Firmware unter Software.

Software ist funktionsfšhig aber noch stark Beta...

Bei Fragen entweder eine E-Mail schicken.

Letzte Änderung am 28.06.2009